# 2ch NIM V/F CONVERTER N2VF-01

(2348 Ver. 3)

SER No.

APPLICATION OF ELECTRONIC DEVICES

## TSUJI ELECTRONICS CO., LTD

3739 Kandatsu-machi Tsuchiura-city Ibaraki-Pref 300-0013 Japan

Phone +81-(0)29-832-3031 fax +81-(0)29-832-2662

URL http://www.tsujicon.jp E-mail info2@tsuji-denshi.co.jp

### NIM V-F CONVERTER USER'S MANUAL

#### Type N2VF-01

A V-F Converter constructed in a NIM-1 UNIT case has two channels outputs and include a four stage amplification factor switch and a polarity selector switch. In addition, with over range and polarity displayed, V-F conversion is always performed at the optimum conditions. The over range signal is output as a transistor open-collector signal which can be used as a warning.

The DC amplifier can be used under isolated (floated) condition from the NIM power source, providing higher noise tolerance.

1. Specification

1) Gain 1MHz/10V, 1MHz/100mV, 1MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 Input Resistance 1M  $\Omega$  or more 1MHz 100v Max) 1 M  $\Omega$  or more 2 TTL level (or out to 50  $\Omega$  by jumper pin) positive logic 0  $\sim$  1MHz 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 M  $\Omega$  or more 1 MHz 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V (Acceptable input  $\pm$  100V Max) 1 MHz/10mV 0  $\sim$  10V Max) 1 MHz/10mV 0  $\sim$

7) Case NIM-1

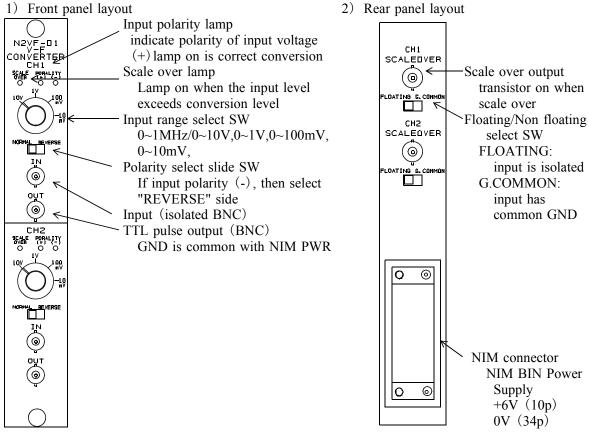

#### 2. Panel lay out

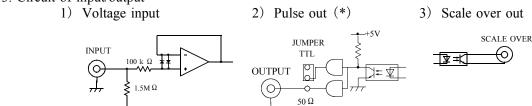

#### 3. Circuit of input/output

(\*) Output level exchange (TTL  $\longleftrightarrow$  50  $\Omega$ ) is enable by opening the left side panel and moving jumper pins (JP3 for ch1, JP4 for ch2) those are located on the front panel side of the board. They are set to TTL level side as defaults.